# **Analog Electronics ENEE236**

Instructor: Nasser Ismail

L8- DC Biasing - BJTs

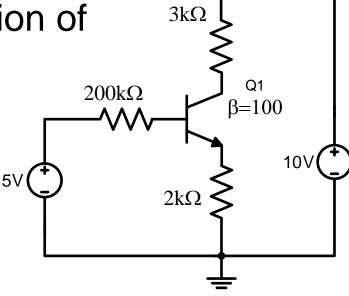

### **Example**

Assume Vce(sat)=0.2 V

Find mode of operation of

Q1?

# Determine Mode of Operation of BJT?

- Solution:

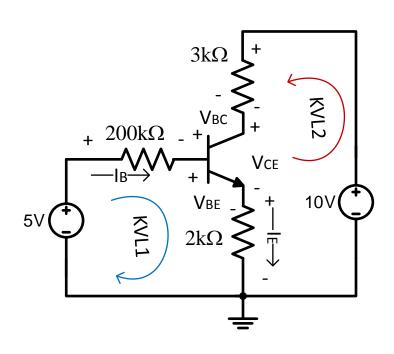

- 1) Since BE junction is forward biased ==> Q1 can be either in Active (Linear) or Saturation mode

- Assume it is in Active Mode

$$5 = 200 \text{ k}\Omega \cdot I_{\text{B}} + V_{\text{BE}} + 2 \text{ k}\Omega \cdot I_{\text{E}}$$

But,

$$I_{\text{E}} = (1 + \beta)I_{\text{B}}$$

Solve for

$$I_B = \frac{5 - V_{BE}}{200 \text{ k}\Omega + (1 + \beta).2 \text{ k}\Omega}$$

$$I_{B} = \frac{5 - 0.7}{200 \text{ k}\Omega + (1 + 100). 2 \text{ k}\Omega}$$

$$= \frac{4.3 \text{ V}}{402 \text{ k}\Omega} = 10.7 \text{ } \mu\text{A}$$

$$I_{C} = \beta I_{B}$$

= (100).(10.7  $\mu$ A)

= 1.07 mA

$I_{E} = (\beta + 1)I_{B}$

= 1.0807 mA

Now we find  $V_{CE}$  from output circuit

10 -

$$I_C$$

.3 k $\Omega$  -  $I_E$  .2 k $\Omega$  =  $V_{CE}$

$\Rightarrow V_{CE} = 4.63 \text{ V} > V_{CE(sat)}$

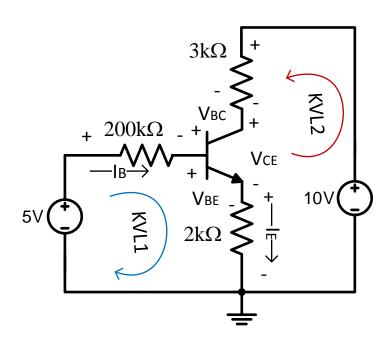

∴ Q1 is in active mode and the assumption is true we can also verify that the BC junction is reverse biassed which is required so that the BJT operates in active mode

$$10 - I_C .3 k\Omega - I_E .2 k\Omega = V_{CE}$$

$$\Rightarrow$$

$V_{CE} = V_{CB} - V_{EB}$

$$\Rightarrow$$

V<sub>CB</sub> = V<sub>CE</sub> - V<sub>BE</sub> = 4.63 - 0.7 = 3.93 V

$$\therefore V_{BC} = -V_{CB} = -3.33 \text{ V}$$

BC junction is reverse biased

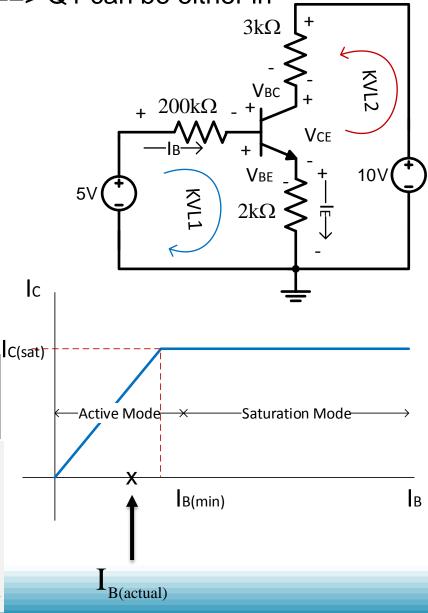

- Solution:

- 1) Since BE junction is forward biased ==> Q1 can be either in Active (Linear) or Saturation mode

- Assume it is in saturation mode:

$$\begin{aligned} &10 - I_{\text{C(sat)}}.3k\Omega - I_{\text{E(sat)}}.2k\Omega = V_{\text{CE(Sat)}} \\ &\text{assume} \quad I_{\text{E(sat)}} = I_{\text{C(sat)}} \\ &\therefore I_{\text{C(sat)}} = \frac{10 - 0.2}{5k\Omega} = 1.96 \text{ mA} \end{aligned}$$

$$I_{B(min)} = \frac{I_{C(sat)}}{\beta} = 19.6 \ \mu A$$

Now we find the actual value of IB

$$I_{B(actual)} = 10.7 \,\mu\text{A}$$

(it was found previously)

since

$I_{\text{B(actual)}} < I_{\text{B(sat)}} = I_{\text{B(min)}} \implies$  the assumption made earlier that BJT in saturation mode is wrong, and actually it is in active mode

### **Biasing**

Biasing: Applying DC voltages to a transistor in order to establish fixed level of voltage and current. For Amplifier (active/Linear) mode, the resulting dc voltage and current establish the operation point to turn it on so that it can amplify AC signals.

### **Operating Point**

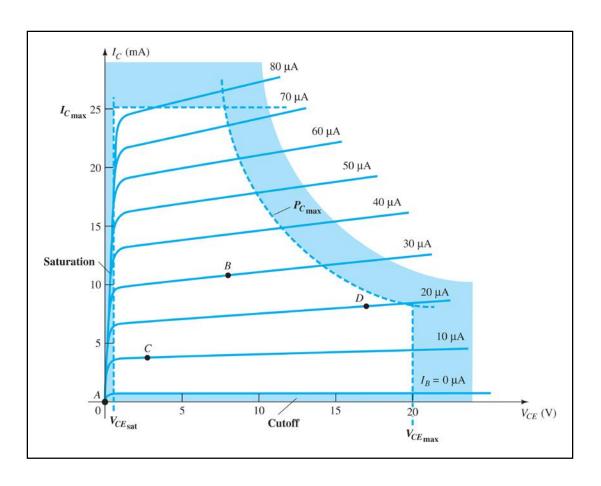

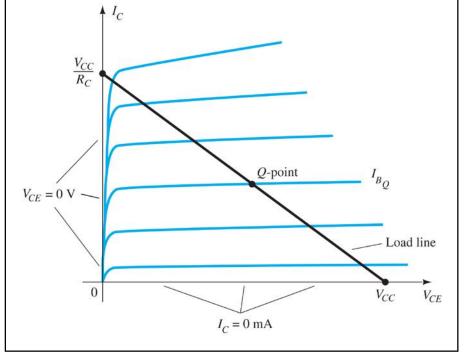

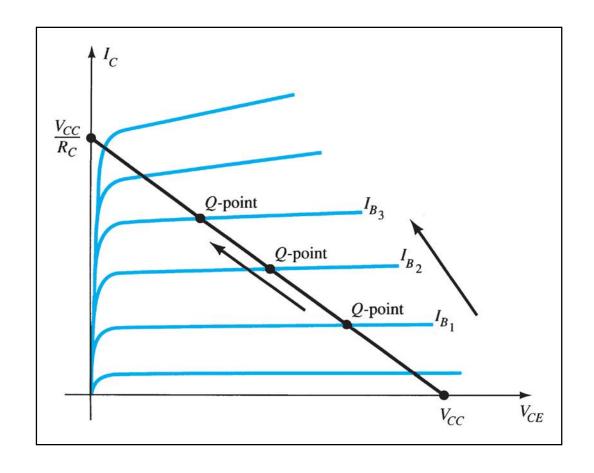

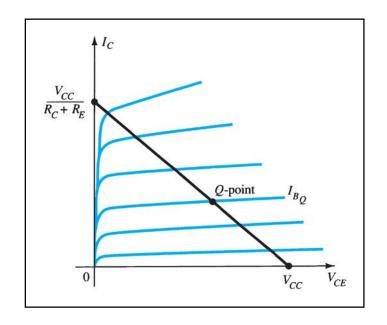

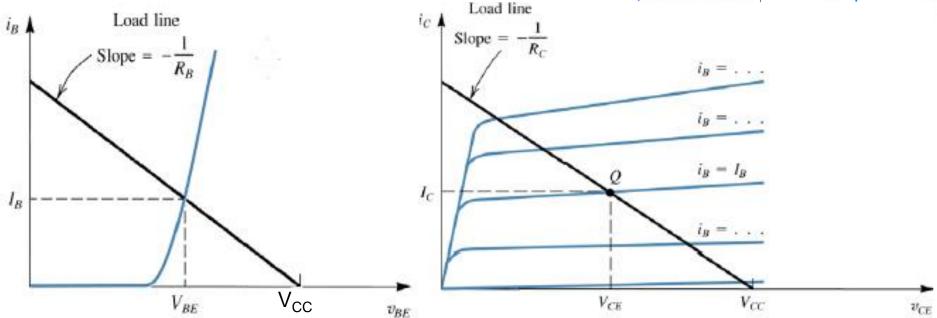

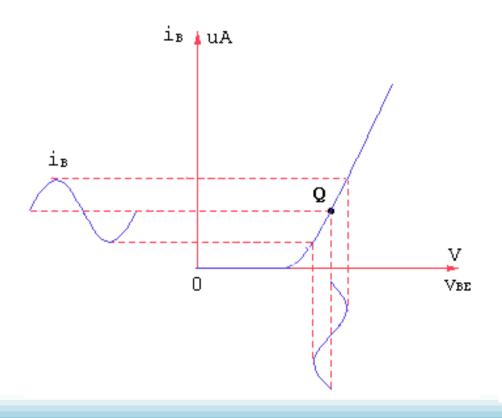

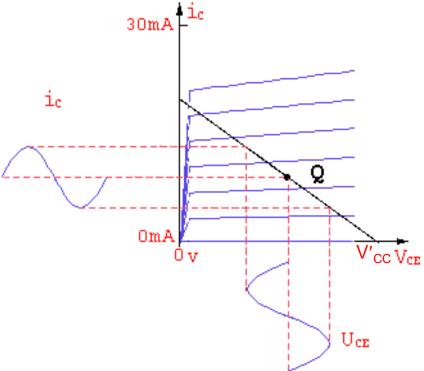

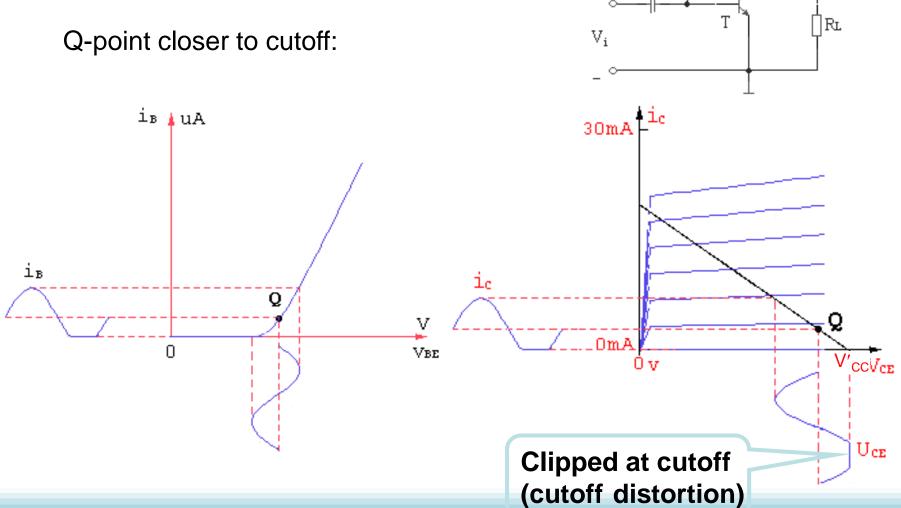

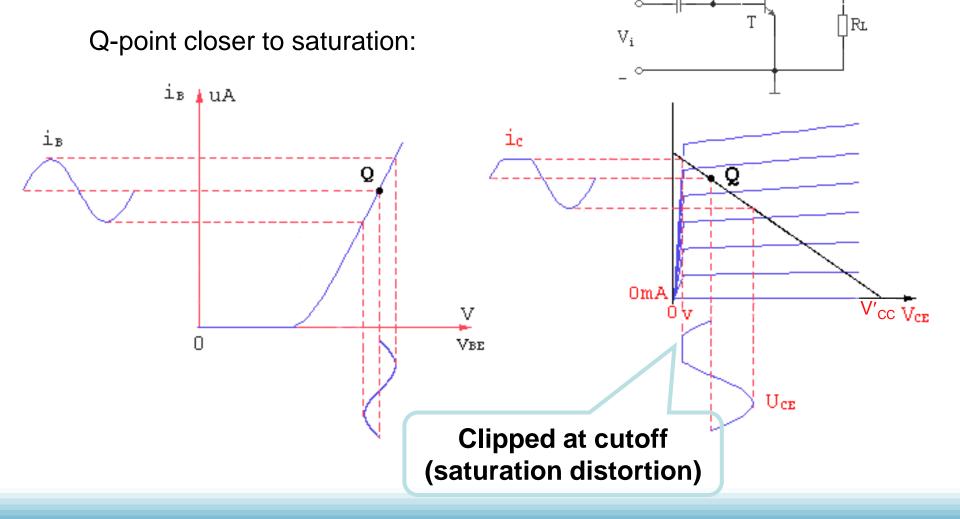

The DC input establishes an operating or quiescent point called the **Q-point**.

### **The Three Operating Regions**

#### **Active or Linear Region Operation**

- Base–Emitter junction is forward biased

- Base–Collector junction is reverse biased

#### **Cutoff Region Operation**

Base–Emitter junction is reverse biased

#### **Saturation Region Operation**

- Base–Emitter junction is forward biased

- Base–Collector junction is forward biased

### **DC Biasing Circuits**

- 1. Fixed-bias circuit

- 2. Emitter-stabilized bias circuit

- 3. DC bias with voltage feedback

- 4. Voltage divider bias circuit

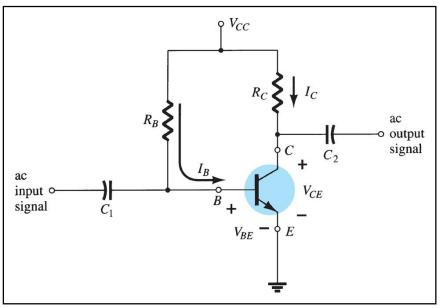

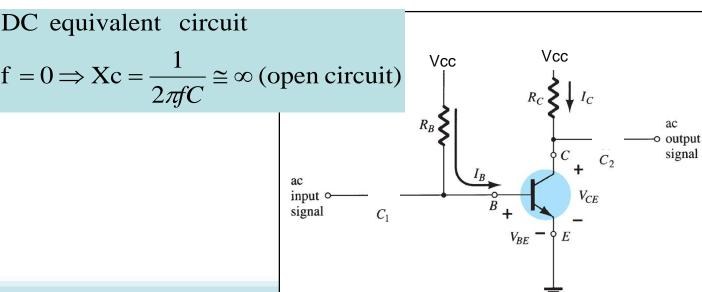

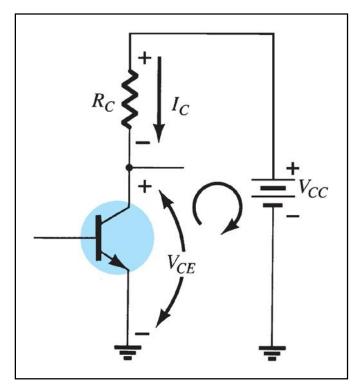

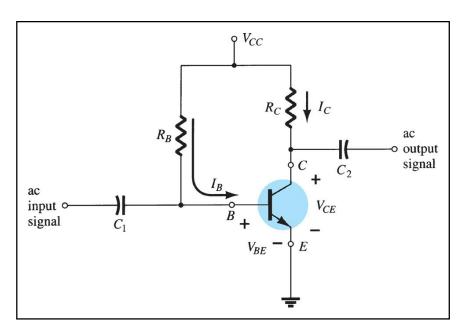

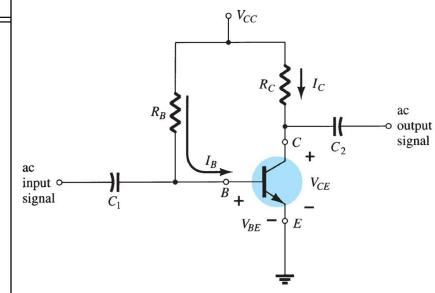

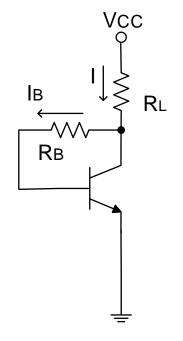

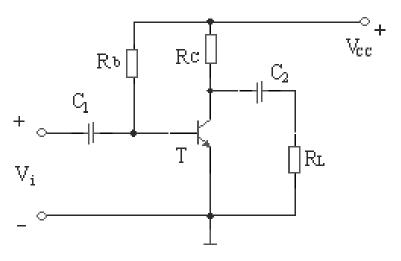

### 1) Fixed Bias Configuration

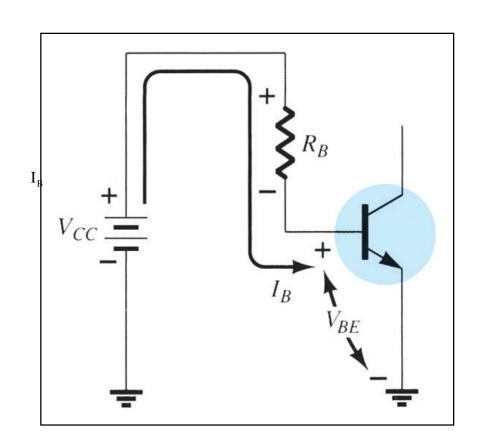

### The Base-Emitter Loop

## From Kirchhoff's voltage law for Input:

$$+ V_{CC} - I_B R_B - V_{BE} = 0$$

#### **Solving for base current:**

$$I_{B} = \frac{V_{CC} - V_{BE}}{R_{B}}$$

Choosing RB will establish the required level of IB

### **Collector-Emitter Loop**

#### **Collector current:**

$$I_C = \beta I_B$$

#### From Kirchhoff's voltage law:

$$V_{CE} = V_{CC} - I_{C}R_{C}$$

$$V_{CE} = V_C - V_E$$

Since

$$V_E = 0$$

$\Longrightarrow :: V_{CE} = V_C$

$$V_{CE} = V_{CC} - I_{C}R_{C}$$

Also

$$V_{BE} = V_{B} - V_{E}$$

$$\therefore V_{BE} = V_{B}$$

$$V_{BE} - V_{CE} - V_{BC} = 0$$

$$V_{BC} - V_{CE} - V_{CE} - V_{CE}$$

$$V_{BC} - V_{CE} - V_{CE} - V_{CE}$$

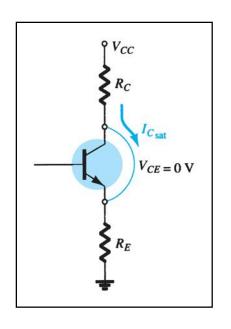

#### **Saturation**

When the transistor is operating in **saturation**, current through the transistor is at its *maximum* possible value.

$$I_{Csat} = \frac{V_{CC}}{R_{C}}$$

$$V_{CE} = V_{CE(sat)} \cong 0 \ V$$

### **Load Line Analysis**

The load line end points are:

#### Csat

$$I_C = V_{CC}/R_C$$

$$V_{CE} = 0 \text{ V}$$

#### **V**<sub>CEcutoff</sub>

$$V_{CE} = V_{CC}$$

$I_C = 0 \text{ mA}$

The Q-point is the operating point where the value of  $R_B$  sets the value of  $I_B$  that controls the values of  $V_{CE}$  and  $I_C$

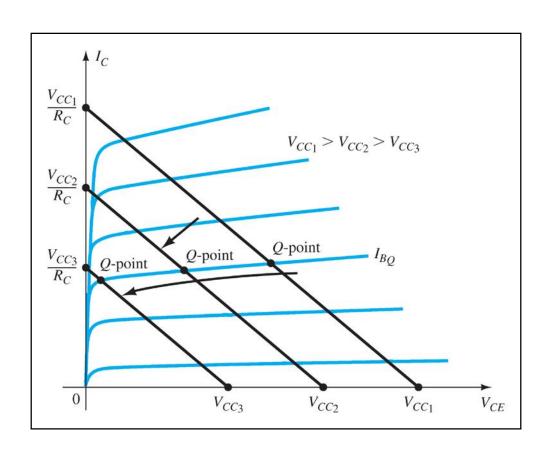

### The Effect of $V_{cc}$ on the Q-Point

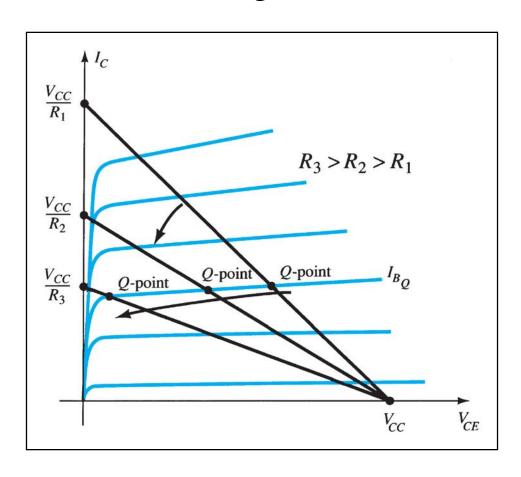

### The Effect of $R_c$ on the Q-Point

### The Effect of $I_B$ on the Q-Point

### Design: Fixed bias

Assume VCC = 10V,  $\beta_{\text{nominal}} = 100$ ,  $\beta_{\text{min}} = 50$ ,  $\beta_{\text{max}} = 150$

Design for Q - point :  $V_{CEQ} = 5V$ ,  $I_{CQ} = 1mA$

#### Solution

$$I_{BQ} = \frac{I_{CQ}}{\beta_{\text{nominal}}} = \frac{1 \text{ mA}}{100} = 10 \text{ }\mu\text{A}$$

$$I_{B} = \frac{V_{CC} - V_{BE}}{R_{B}} \Longrightarrow$$

$$R_{B} = \frac{V_{CC} - V_{BE}}{I_{B}} = \frac{10 - 0.7}{10 \,\mu\text{A}}$$

$$=930 k\Omega$$

$$V_{CE} = V_{CC} - I_{C}R_{C}$$

$$V_{CEQ} = 5 = 10 - I_{C}R_{C}$$

$$\therefore R_C = \frac{5}{1 \text{ mA}} = 5 \text{ k}\Omega$$

### **Fixed bias Stability**

Assume VCC = 10V,  $\beta_{\text{nominal}} = 100$ ,  $\beta_{\text{min}} = 50$ ,  $\beta_{\text{max}} = 100$

Design for Q - point :  $V_{CEO} = 5V$ ,  $I_{CO} = 1mA$

Solution – continued

If

$$\beta = \beta_{min} = 50$$

$$I_{\rm B} = 10 \, \mu A$$

$$I_C = \beta I_B = (50)(10 \,\mu\text{A}) = 0.5 \,\text{mA}$$

$$V_{CE} = V_{CC} - I_{C}R_{C}$$

$$V_{CEO} = 10 - (0.5 \text{ mA})(5 \text{ k}\Omega) = 7.5 \text{ V}$$

If

$$\beta = \beta_{max} = 150$$

$$I_{\rm R} = 10 \, \mu A$$

$$I_C = \beta I_B = (150)(10 \,\mu\text{A}) = 1.5 \,\text{mA}$$

$$V_{CE} = V_{CC} - I_{C}R_{C}$$

$$V_{CEQ} = 10 - (1.5 \text{ mA})(5 \text{ k}\Omega) = 2.5 \text{ V}$$

for

$$50 \le \beta \le 150$$

$$I_{\rm B} = 10 \,\mu A$$

fixed

$$0.5 \,\mathrm{mA} \leq \,\mathrm{I}_{\mathrm{C}} \leq 1.5 \,\mathrm{mA}$$

$$7.5 \text{ V} \ge \text{ V}_{CE} \ge 2.5 \text{ V}$$

$$\therefore \frac{I_{C(max)}}{I_{C(max)}} = \frac{1.5 \text{ mA}}{0.5 \text{ mA}} = 3$$

Not very stable

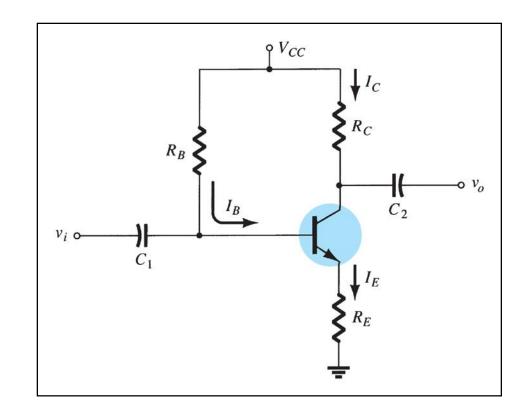

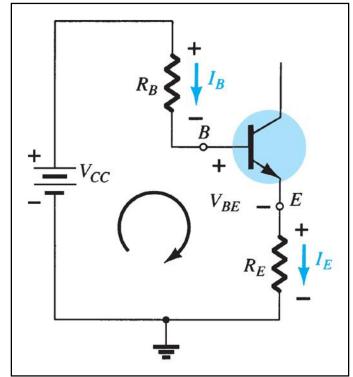

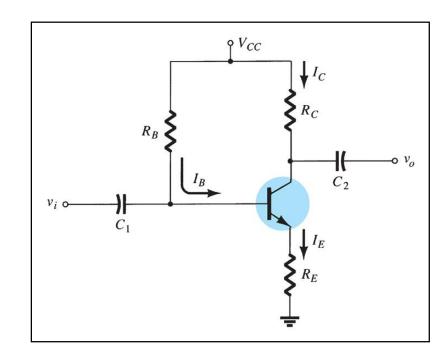

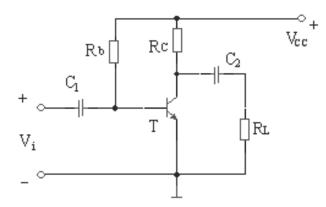

### 2) Emitter-Stabilized Bias Circuit

Adding a resistor  $(R_E)$  to the emitter circuit stabilizes the bias circuit.

### **Base-Emitter Loop**

#### From Kirchhoff's voltage law:

$$+V_{CC}-I_BR_B-V_{BE}-I_ER_E = 0$$

Since

$$I_E = (\beta + 1)I_B$$

:

$$V_{CC} - I_B R_B - V_{BE} - (\beta + 1) I_B R_E = 0$$

#### Solving for I<sub>B</sub>:

$$I_B = \frac{V_{CC} - V_{BE}}{R_B + (\beta + 1)R_E}$$

$(\beta + 1)R_E \leftarrow$  is the emitter resistor as it appears in the base emitter loop

### **Base-Emitter Loop**

#### Solving for I<sub>E</sub>:

$$I_E = \frac{V_{CC} - V_{BE}}{\frac{R_B}{(\beta + 1)} + R_E}$$

In order to get IE almost independant of B we choose:

$$R_E >> \frac{R_B}{(\beta + 1)}$$

$$\Rightarrow I_E \cong \frac{V_{CC} - V_{BE}}{R_E}$$

Also, in order to guarantee operation in linear mode

we choose

$$0.1 V_{CC} \le V_{E} < 0.2 V_{CC}$$

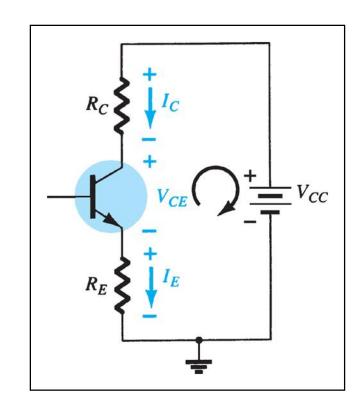

### **Collector-Emitter Loop**

From Kirchhoff's voltage law:

$$I_E R_E + V_{CE} + I_C R_C - V_{CC} = 0$$

Since  $I_E \cong I_C$ :

$$V_{CE} = V_{CC} - I_C(R_C + R_E)$$

Also:

$$V_E = I_E R_E$$

$$V_C = V_{CE} + V_E = V_{CC} - I_C R_C$$

$$V_B = V_{CC} - I_R R_B = V_{BE} + V_E$$

### Design: Emitter Stabilization bias

Assume VCC = 10V,  $\beta_{\text{nominal}} = 100$ ,  $\beta_{\text{min}} = 50$ ,  $\beta_{\text{max}} = 150$

Design for Q - point :  $V_{CEQ} = 5V$ ,  $I_{CQ} = 1mA$

Solution

$$-let V_E = 0.1 V_{CC}$$

$$V_E = 1V$$

$$I_E = \frac{V_E}{R_E} \Longrightarrow R_E = \frac{1 \text{ V}}{1.01 \text{ mA}} \cong 1 \text{ k}\Omega$$

$$I_B = \frac{V_{CC} - V_{BE}}{R_- + (\beta + 1)R_-} \Longrightarrow$$

$$R_{\scriptscriptstyle B}I_{\scriptscriptstyle B} + I_{\scriptscriptstyle B}(\beta+1)R_{\scriptscriptstyle E} = V_{\scriptscriptstyle CC} - V_{\scriptscriptstyle BE}$$

$$R_{B} = \frac{V_{CC} - V_{BE} - I_{B}(\beta + 1)R_{E}}{I_{B}}$$

$$= \frac{10 - 0.7 - 10 \,\mu A(100 + 1)1 \,k\Omega}{10 \,\mu A}$$

$$V_{CE} = V_{CC} - I_{C}R_{C} - V_{E}$$

$$V_{CEQ} = 5 = 10 - 1 - I_{C}R_{C}$$

$$\therefore R_{\rm C} = \frac{4}{1 \, \text{mA}} = 4 \, \text{k}\Omega$$

$= 829 \text{ k}\Omega$

### **Emitter bias Stability**

If

$$\beta = \beta_{min} = 50$$

$$I_{B} = \frac{9.3}{829k\Omega + 51k\Omega} = 10.56 \,\mu\text{A}$$

$$I_{C} = \beta I_{B} = (50)(10.56 \,\mu\text{A}) = 0.528 \,\text{mA}$$

$$V_{CE} = V_{CC} - I_{C}R_{C} - V_{E}$$

$$V_{CEQ} = 10 - (0.528 \text{ mA})(4 \text{ k}\Omega) - 1 = 6.89 \text{ V}$$

If

$$\beta = \beta_{max} = 150$$

$$I_{\rm B} = \frac{9.3}{829k\Omega + 151k\Omega} = 9.489 \,\mu{\rm A}$$

$$I_C = \beta I_B = (150)(9.489 \,\mu\text{A}) = 1.423 \,\text{mA}$$

$$V_{CE} = V_{CC} - I_C R_C - V_E$$

$$V_{CEQ} = 10 - (1.423 \text{ mA})(4 \text{ k}\Omega) - 1 = 3.31 \text{ V}$$

for

$$50 \le \beta \le 150$$

$$10.56 \,\mu\text{A} \ge I_{\text{B}} \ge 9.489 \,\mu\text{A}$$

$$0.528 \,\mathrm{mA} \le I_{\rm C} \le 1.423 \,\mathrm{mA}$$

$$6.89 \text{ V} \ge \text{ V}_{CE} \ge 3.31 \text{ V}$$

$$\therefore \frac{I_{C(max)}}{I_{C(min)}} = \frac{1.423 \text{ mA}}{0.528 \text{ mA}} \cong 2.7$$

Improved, but not very stable

### **Improved Biased Stability**

**Stability** refers to a condition in which the currents and voltages remain fairly constant over a wide range of temperatures and transistor Beta ( $\beta$ ) values.

Adding  $R_E$  to the emitter improves the stability of a transistor.

### Saturation Level

The endpoints can be determined from the load line.

$$V_{CE} = V_{CC}$$

$I_C = 0 \text{ mA}$

$$V_{CE} = 0 \text{ V}$$

$$I_C = \frac{V_{CC}}{R_C + R_E}$$

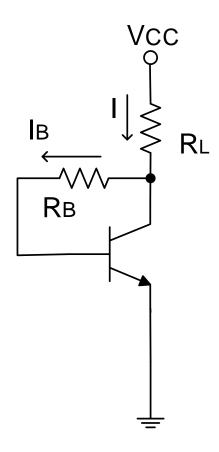

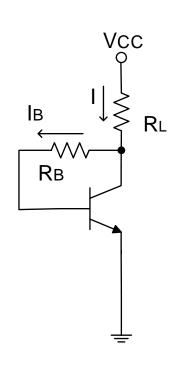

### 3) DC Bias With Voltage Feedback

Another way to improve the stability of a bias circuit is to add a feedback path from collector to base.

In this bias circuit the Q-point is only slightly dependent on the transistor beta,  $\beta$ .

### **Base-Emitter Loop**

#### From Kirchhoff's voltage law:

$$\begin{split} &V_{CC}-I.R_L-I_BR_B-V_{BE}=0\\ &I=I_C+I_B\\ &I_C=\beta I_B \end{split}$$

#### Solving for $I_B$ :

$$I_{B} = \frac{V_{CC} - V_{BE}}{R_{L}(\beta + 1) + R_{B}}$$

$$\begin{split} &V_{\text{CC}} = I.R_{\text{L}} + V_{\text{CE}} \\ &I = I_{\text{C}} + I_{\text{B}} \\ &V_{\text{CE}} = V_{\text{CC}} - \left(I_{\text{C}} + I_{\text{B}}\right) R_{\text{L}} \end{split}$$

suppose

$$\beta \uparrow$$

,  $I_B \downarrow$ ,  $I_C = \uparrow \beta . I_B \downarrow \cong const$

there is some kind of compensation effect

### Design: Voltage feedback bias

Assume VCC = 10V,

$$\beta_{\text{nominal}} = 100$$

,  $\beta_{\text{min}} = 50$ ,  $\beta_{\text{max}} = 150$

Design for Q - point :  $V_{CEO} = 5V$ ,  $I_{CO} = 1mA$

$=4.95 \mathrm{k}\Omega$

Solution

$$R_{L} = \frac{V_{CC} - V_{CE}}{I_{C} + I_{B}} = \frac{10 - 5}{1mA + \frac{1mA}{100}}$$

$$I_{B} = \frac{V_{CC} - V_{BE}}{R_{L}(\beta + 1) + R_{B}}$$

$$\therefore R_{\rm B} = 430 \,\mathrm{k}\Omega$$

If

$$\beta = \beta_{min} = 50$$

$$I_{\rm B} = 0.013627 \, \text{mA}$$

$$I_{\rm C} = 0.68 \, \text{mA}$$

If

$$\beta = \beta_{max} = 150$$

$$I_B = 0.00793 \,\text{mA}$$

$$I_{\rm C} = 1.19 \, \rm mA$$

for

$$50 \le \beta \le 150$$

$$0.68 \, \text{mA} \le I_{\text{C}} \le 1.19 \, \text{mA}$$

$$\therefore \frac{I_{C(max)}}{I_{C(min)}} = \frac{1.19 \text{ mA}}{0.68 \text{ mA}} \cong 1.75$$

Better Q-point stability

### **Base-Emitter Bias Analysis**

#### **Transistor Saturation Level**

$$I_{Csat} = I_{Cmax} = \frac{V_{CC}}{R_{L}}$$

## Load Line Analysis Cutoff

$$V_{CE} = V_{CC}$$

$I_C = 0 \, mA$

#### **Saturation**

$$I_{C} = \frac{V_{CC}}{R_{L}}$$

$$V_{CE} = 0 \text{ V}$$

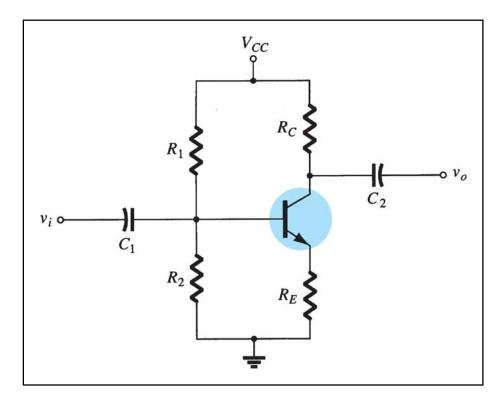

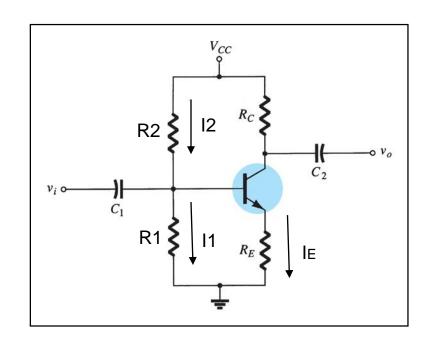

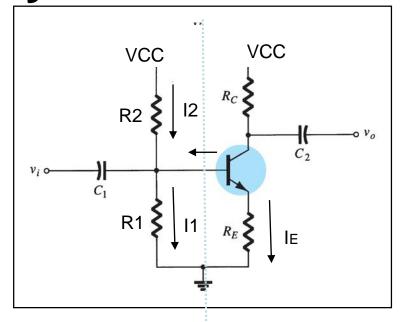

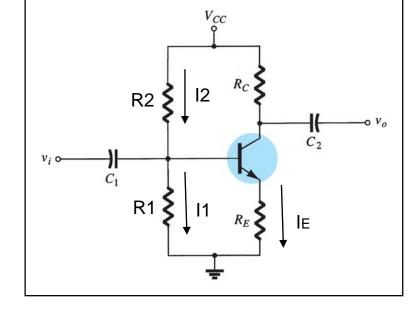

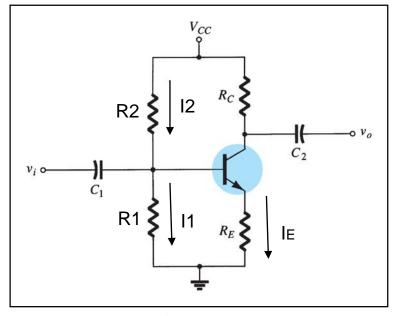

### 4) Voltage Divider Bias

This is a very stable bias circuit.

The currents and voltages are nearly independent of any variations in  $\beta$  if the circuit is designed properly

### **Approximate Analysis**

#### Where $I_B \ll I_1$ and $I_1 \cong I_2$ :

$$V_{B} = \frac{R_1 V_{CC}}{R_1 + R_2}$$

$$V_{E} = V_{B} - V_{BE}$$

$$I_{\text{E(approximate)}} = \frac{V_{E}}{R_{E}} = \frac{V_{B} - V_{BE}}{R_{E}}$$

#### From Kirchhoff's voltage law:

$$V_{CE} = V_{CC} - I_C R_C - I_E R_E$$

$$I_E \cong I_C$$

$$V_{CE} = V_{CC} - I_C (R_C + R_E)$$

Here we got Ic independent of β which provides good Q-point stability

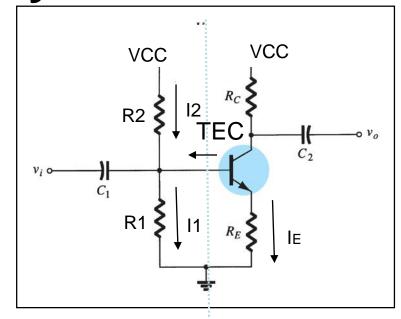

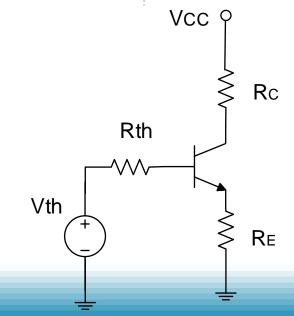

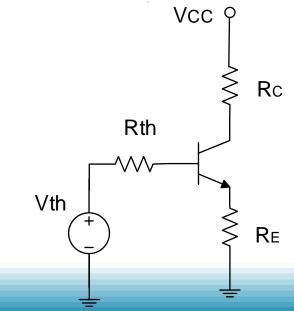

### **Exact Analysis**

We must try to make  $I_B$  as close as possible to zero

Thevenin Equivalent circuit for the circuit left of the base is done R<sub>1</sub>V<sub>CC</sub>

$$V_{th} = \frac{R_1 V_{CC}}{R_1 + R_2}$$

$$R_{th} = R_1 // R_2 = \frac{R_1 R_2}{R_1 + R_2}$$

$$\boldsymbol{V}_{th} = \boldsymbol{I}_{B}\boldsymbol{R}_{th} + \boldsymbol{V}_{BE} + \boldsymbol{I}_{E}\boldsymbol{R}_{E}$$

but

$$I_B = \frac{I_E}{\beta + 1}$$

$$\therefore I_{E(exact)} = \frac{V_{th} - V_{BE}}{\frac{Rth}{\beta + 1} + R_{E}}$$

### **Exact Analysis**

$$\therefore I_{E(exact)} = \frac{V_{th} - V_{BE}}{\frac{Rth}{\beta + 1} + R_{E}}$$

if we compare to approximate solution

$$I_{\text{E(approximate)}} = \frac{V_{\text{B}} - V_{\text{BE}}}{R_{\text{E}}}$$

$\Rightarrow$  we must make the quantity  $\frac{\text{Rth}}{\beta + 1} \ll R_E$

#### Here we got Ic independent of $\beta$

$$\therefore \text{ Rth} << (\beta+1)R_E$$

as a rule let Rth  $<< \frac{(\beta+1)R_E}{10}$

or

$$\beta R_E$$

# Design: Voltage Divider bias

Assume VCC = 10V,  $\beta_{\text{nominal}} = 100$ ,  $\beta_{\text{min}} = 50$ ,  $\beta_{\text{max}} = 150$

Design for Q - point :  $V_{CEQ} = 5V$ ,  $I_{CQ} = 1mA$

Solution

1) let

$$V_E = 0.1 V_{CC}$$

$$V_E = 1V$$

$$I_E = \frac{V_E}{R_E} \Longrightarrow R_E = \frac{1 \text{ V}}{1.01 \text{ mA}} \cong 1 \text{ k}\Omega$$

2) let Rth =

$$\frac{R_E.\beta_{\text{nominal}}}{50} = \frac{1 \text{ k}\Omega.100}{50} = 2 \text{ k}\Omega$$

3)

$$V_{CC} = R_C I_C + I_E R_E + V_{CE}$$

$V_{CEO} = 5$

$$\therefore R_{C} = \frac{V_{CC} - V_{CE} - V_{E}}{1mA} = \frac{10 - 5 - 1}{1mA} = 4 k\Omega$$

# Design: Voltage Divider bias

Assume VCC = 10V,

$$\beta_{\text{nominal}} = 100$$

,  $\beta_{\text{min}} = 50$ ,  $\beta_{\text{max}} = 150$

Design for Q - point :  $V_{CEO} = 5V$ ,  $I_{CO} = 1mA$

Solution – continued

$$4)I_{E} = \frac{V_{th} - V_{BE}}{\frac{Rth}{\beta + 1} + R_{E}}$$

$$\therefore V_{th} = \frac{R_1 V_{CC}}{R_1 + R_2} = I_E \left( \frac{Rth}{\beta + 1} + R_E \right) + V_{BE} = 1.72 V \dots (1)$$

$$R_{th} = R_1 // R_2 = \frac{R_1 R_2}{R_1 + R_2} = 2 k\Omega$$

solving (1) & (2) yields:

$$R_1 = 2.42 \text{ k}\Omega$$

$$R_2 = 11.64 \text{ k}\Omega$$

# Voltage Divider bias Stability

If

$$\beta = \beta_{min} = 50$$

$$I_{\rm C} = 0.982 \, \text{mA}$$

If

$$\beta = \beta_{\text{max}} = 150$$

$$I_{\rm C} = 1.0069 \, \text{mA}$$

for

$$50 \le \beta \le 150$$

$$0.982 \,\mathrm{mA} \le \,\mathrm{I_C} \le 1.0067 \,\mathrm{mA}$$

$$\therefore \frac{I_{C(max)}}{I_{C(min)}} = \frac{1.0067 \text{ mA}}{0.982 \text{ mA}} \cong 1.0254$$

Very good Q-point stability

# **Voltage Divider Bias Analysis**

#### **Transistor Saturation Level**

$$I_{Csat} = I_{Cmax} = \frac{V_{CC}}{R_C + R_E}$$

#### **Load Line Analysis**

#### **Cutoff:**

$$V_{CE} = V_{CC}$$

$I_C = 0 \text{ mA}$

#### **Saturation:**

$$I_C = \frac{V_{CC}}{R_C + R_E}$$

$$V_{CE} = 0 \text{ V}$$

#### **PNP Transistors**

The analysis for *pnp* transistor biasing circuits is the same as that for *npn* transistor circuits. The only difference is that the currents are flowing in the opposite direction.

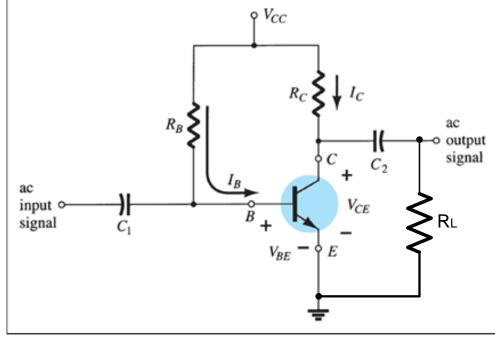

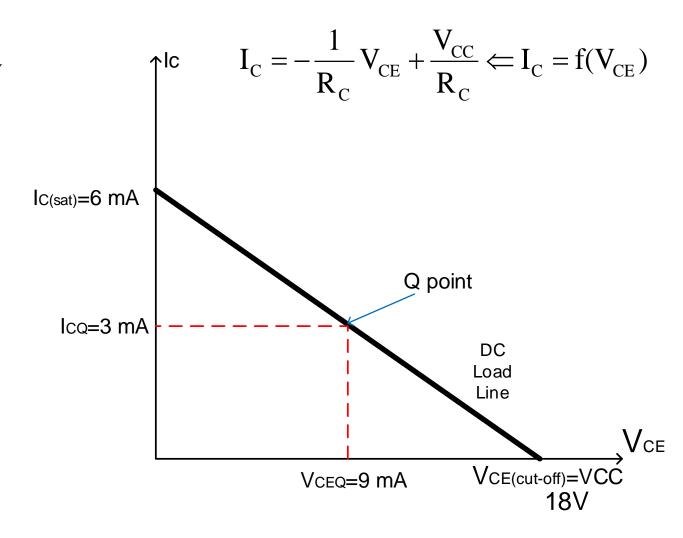

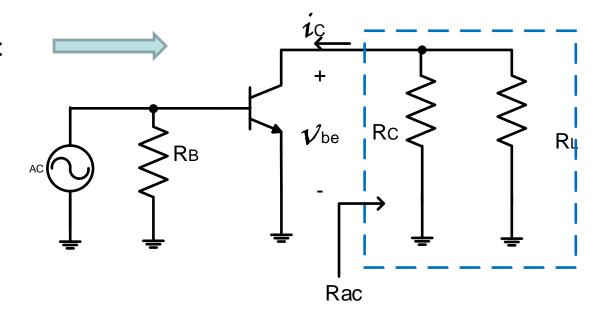

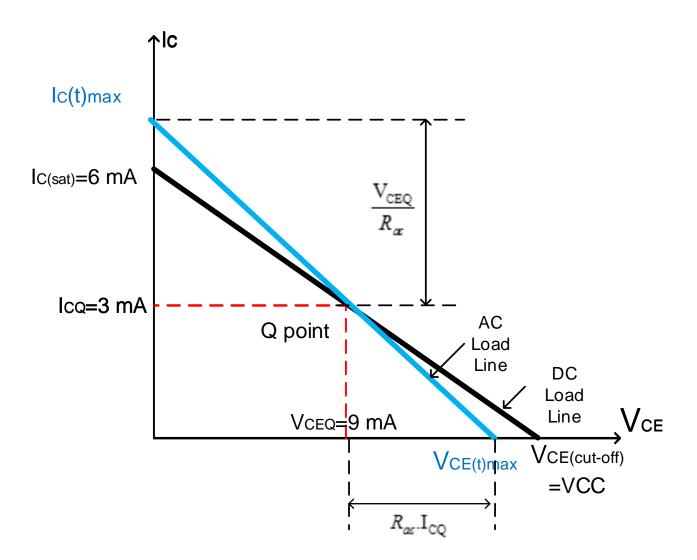

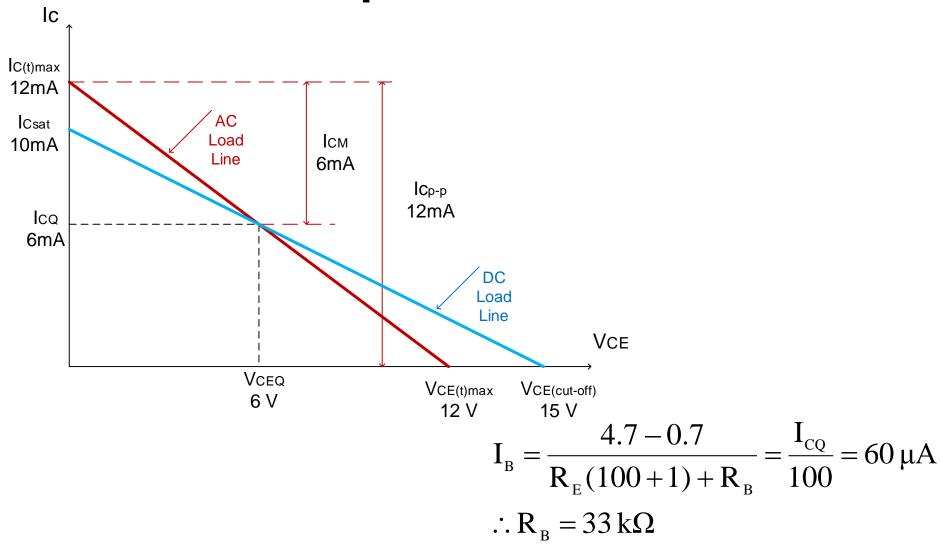

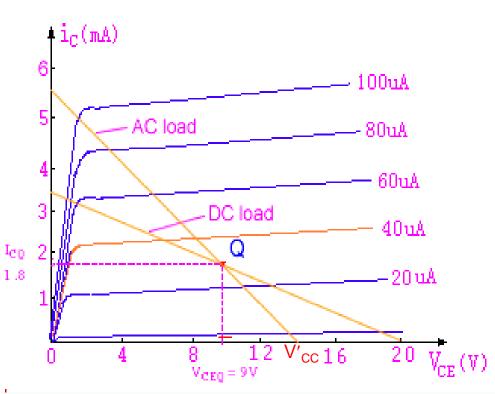

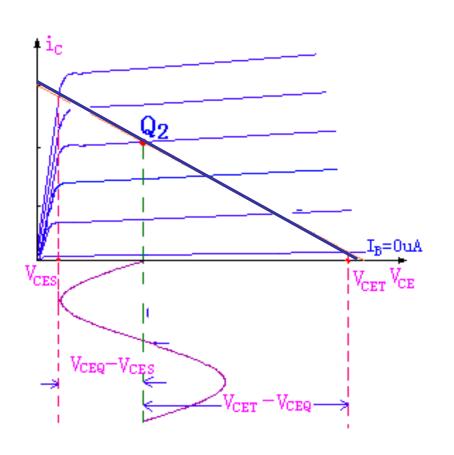

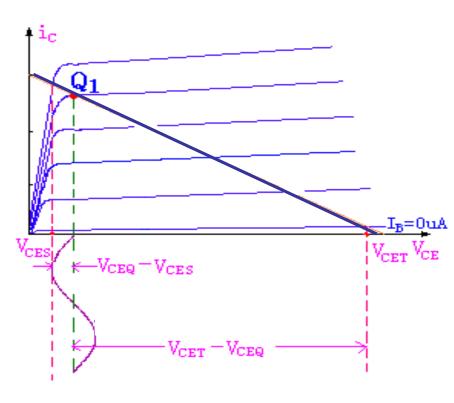

#### DC and AC Load Lines

Assume VCC = 18V,  $\beta$  = 100

$$R_{\rm B} = 576 \, k\Omega; R_{\rm C} = 3k\Omega; V_{\rm BE} = 0.65 \, V$$

FIRST: DC ANALYSIS

$$V_{CC} = V_{CE} + I_{C}R_{C}$$

$$I_{C} = -\frac{1}{R_{C}}V_{CE} + \frac{V_{CC}}{R_{C}} \Leftarrow I_{C} = f(V_{CE})$$

This is a straight line equation

$$Y = mX + b$$

$$I_{B} = \frac{V_{CC} - V_{BE}}{R_{B}} = \frac{18 - 0.65}{576 \text{ k}\Omega} = 30 \,\mu\text{A}$$

$$I_{C} = \beta I_{B} = 3 \text{ mA}$$

$$V_{CE} = V_{CC} - I_{C}R_{C} = 18 - (3\text{mA})(3\text{k}\Omega)$$

$$= 9 \text{ V}$$

#### Csat

$$I_{Csat} = \frac{V_{CC}}{R_{C}}$$

$$V_{CE} = V_{CE(sat)} \cong 0 \ V$$

#### **V**<sub>CEcutoff</sub>

$$V_{CE(cutoff)} = V_{CC}$$

$I_C = 0 \text{ mA}$

#### **DC Load Line**

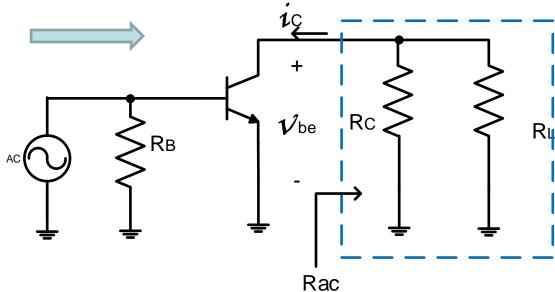

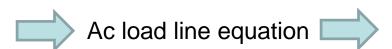

#### **AC Load Line**

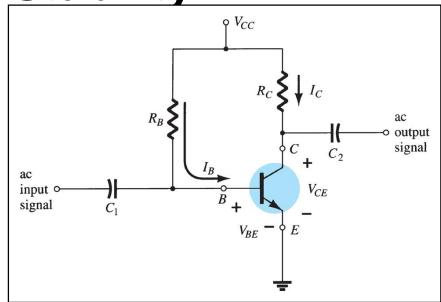

#### **AC Equivalent Circuit**

Since we have dc and ac quantities,

let us define the notation

total DC ac

$$V_{BE}(t) = V_{BE} + v_{be}$$

$$V_{CE}(t) = V_{CE} + v_{ce}$$

$$I_C(t) = I_C + i_C$$

$$I_{B}(t) = I_{B} + i_{b}$$

$$v_{ce} = -R_{ac}.i_c$$

where

$$R_{ac} = R_c // R_L$$

is the ac resistance seen from collector terminal

+ resistance seen from emitter terminal

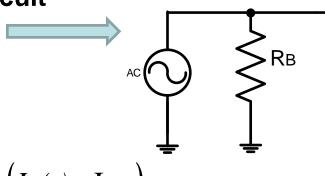

#### **AC Load Line**

#### **AC Equivalent Circuit**

$$v_{ce} = V_{CE}(t) - V_{CE}$$

$$i_{c} = I_{C}(t) - I_{C}$$

$$v_{ce} = -R_{ac}.i_c$$

To Draw ac load line we find  $(V_{CE}(t)_{max})$  and  $(I_{C}(t)_{max})$

#### **AC Load Line**

$$(V_{CE}(t) - V_{CEQ}) = -R_{ac} \cdot (I_C(t) - I_{CQ})$$

$$(V_{CE}(t)_{\text{max}} - V_{CEQ}) = R_{ac} \cdot I_{CQ}$$

$$V_{CE}(t)_{\text{max}} = V_{CEQ} + R_{ac} \cdot I_{CQ}$$

, when  $I_{C}(t) = 0$

$$(V_{CE}(t) - V_{CEQ}) = -R_{ac} \cdot (I_C(t) - I_{CQ})$$

$$I_{C}(t)_{\text{max}} = \frac{V_{\text{CEQ}}}{R_{\text{ce}}} + I_{\text{CQ}} \text{ when } V_{\text{CE}}(t) = 0$$

## Design

- In order to have the amplifier to amplify an input ac signal without distortion (by going into saturation or cut-off)

- We choose the Q-point in the middle of ac load line

$$I_{CQ} = \frac{1}{2} I_C(t)_{max}$$

$$V_{CEQ} = \frac{1}{2} V_{CE}(t)_{max}$$

$$2I_{CQ} = I_{C}(t)_{max}$$

$$2I_{CQ} = I_{CQ} + \frac{V_{CEQ}}{R_{ac}}$$

$$\therefore I_{CQ} = \frac{V_{CEQ}}{R}$$

# DC Analysis

$$V_{CC} = V_{CE} + I_{C}R_{C}$$

define  $R_{dc} = R_{C}$

$$V_{CC} = V_{CE} + I_{C}R_{dc}$$

at the Q - point

$$V_{\text{CC}} = V_{\text{CEQ}} + I_{\text{CQ}} R_{\text{dc}}$$

For maximum Symmetrical swing

$$\begin{split} \mathbf{I}_{\mathrm{CQ}} &= \frac{\mathbf{V}_{\mathrm{CEQ}}}{R_{ac}} \Rightarrow \mathbf{V}_{\mathrm{CEQ}} = \mathbf{I}_{\mathrm{CQ}} R_{ac} \\ \mathbf{V}_{\mathrm{CC}} &= \mathbf{I}_{\mathrm{CQ}}.\mathbf{R}_{ac} + \mathbf{I}_{\mathrm{CQ}}.\mathbf{R}_{\mathrm{dc}} \\ & \therefore \mathbf{I}_{\mathrm{CQ}} = \frac{V_{CC}}{\mathbf{R}_{ac} + \mathbf{R}_{dc}} \end{split} \qquad \text{To design for maximum Symmetrical Swing}$$

## **DC** Analysis

Also

$$\begin{split} &V_{\text{CEQ}} = V_{\text{CC}} - I_{\text{CQ}} R_{\text{dc}} \\ &= V_{\text{CC}} - R_{\text{dc}} \frac{V_{\text{CC}}}{R_{\text{ac}} + R_{\text{dc}}} \\ &= V_{\text{CC}} \left( 1 - \frac{R_{\text{dc}}}{R_{\text{ac}} + R_{\text{dc}}} \right) \\ &= V_{\text{CC}} \left( \frac{R_{\text{ac}} + R_{\text{dc}} - R_{\text{dc}}}{R_{\text{ac}} + R_{\text{dc}}} \right) \\ &= V_{\text{CC}} \left( \frac{R_{\text{ac}} + R_{\text{dc}} - R_{\text{dc}}}{R_{\text{ac}} + R_{\text{dc}}} \right) \\ &= V_{\text{CC}} \left( \frac{R_{\text{ac}}}{R_{\text{ac}} + R_{\text{dc}}} \right) = \left( \frac{V_{\text{CC}}}{1 + \frac{R_{\text{dc}}}{R}} \right)^{*****For maximum Symmetrical swing} \end{split}$$

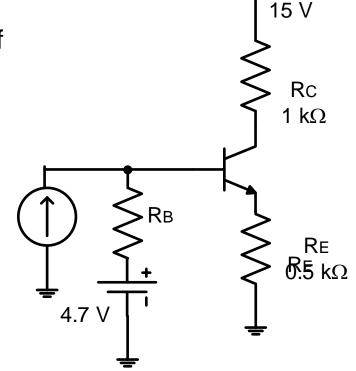

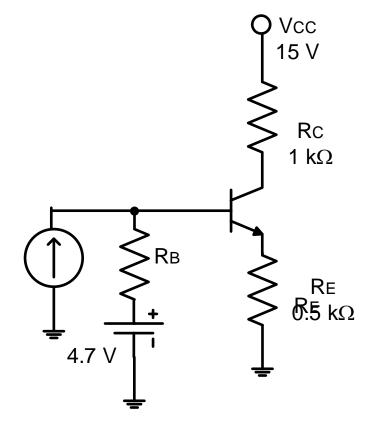

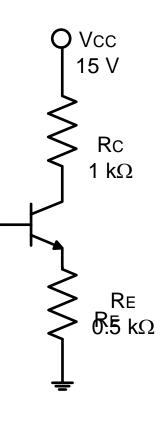

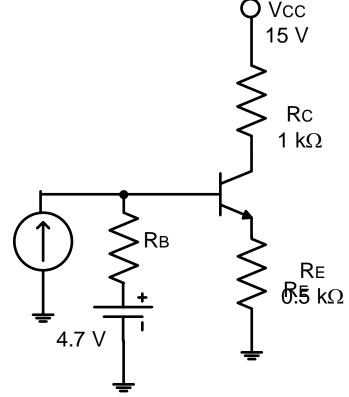

# **Design Example**

Design for maximum symmetrical swing of the collector current? Find the Q-point? Find the required Value of RB? Draw AC and DC load lines What is the power dissipation of the transistor at the Q-point?

Vcc

#### **Solution**

$$R_{ac} = R_{C} = 1 \text{ k}\Omega$$

$$R_{dc} = R_C + R_E = 1.5 \text{ k}\Omega$$

For Maximum Symmetrical Swing of Ic

$$I_{CQ} = \frac{V_{CC}}{R_{ac} + R_{dc}} = \frac{15}{1 \text{ k}\Omega + 1.5 \text{ k}\Omega} = 6 \text{ mA}$$

$$V_{CEQ} = \frac{V_{CC}}{1 + \frac{R_{dc}}{R_{gc}}} = \frac{15}{1 + \frac{1.5 \text{ k}\Omega}{1 \text{ k}\Omega}} = 6 \text{ V}$$

Maximum Swing (peak) of Ic

$$I_{\rm CM} = I_{\rm CQ} = 6 \, \text{mA}$$

Maximum Symmetrical Swing (peak - peak) of Ic

$$I_{Cp-p} = 2I_{CQ} = 12 \text{ mA}$$

# **Solution**

For Maximum Symmetrical Swing of Ic

$$I_{C}(t)_{Max} = I_{CQ} + \frac{V_{CEQ}}{R_{ac}} = 6 \text{ mA} + \frac{6}{1 \text{ k}\Omega} = 12 \text{ mA}$$

For Maximum Symmetrical Swing of Ic

$$V_{CE}(t)_{Max} = I_{CQ}R_{ac} + V_{CEQ} = 6 \text{ mA.} 1 \text{ k}\Omega + 6 = 12 \text{ V}$$

### **Example -Continued**

$$P_0 = V_{CEO} I_{CO} = 6V. 6mA = 36 mW$$

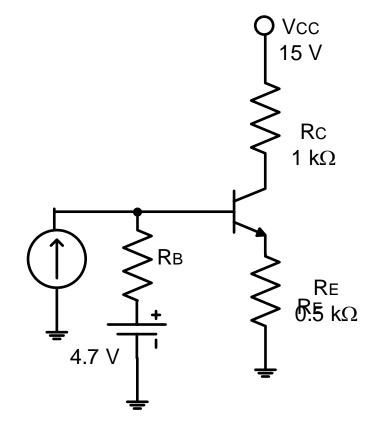

#### **Analysis Example**

RB=50  $k\Omega$ Find the maximum collector current swing and the Q-point? Draw AC and DC load lines What is the power dissipation of the transistor at the Q-point?

$$R_{ac} = R_{C} = 1 k\Omega$$

$$R_{dc} = R_C + R_E = 1.5 \text{ k}\Omega$$

# **Solution**

Value of Ic

$$I_{B} = \frac{4.7 - 0.7}{R_{E}(100 + 1) + R_{B}}$$

$$=\frac{4.7-0.7}{500(100+1)+50k\Omega}$$

$$=40 \,\mu\text{A}$$

$$I_{CO} = \beta I_{BO} = 4 \text{ mA}$$

$$V_{CEQ} = V_{CC} - I_{CQ} (R_C + R_E) = 9 V$$

Maximum Swing (peak) of Ic

$$I_{CM} \neq I_{CO}$$

$$I_{CM} = 4 \text{ mA}$$

Maximum Symmetrical Swing (peak - peak) of Ic

$$I_{Cp-p} = 2I_{CM} = 8 \text{ mA}$$

# **Solution**

$$I_{C}(t)_{Max} = I_{CQ} + \frac{V_{CEQ}}{R_{ac}} = 4 \text{ mA} + \frac{9}{1 \text{ k}\Omega} = 13 \text{ mA}$$

$$V_{CE}(t)_{Max} = I_{CQ}R_{ac} + V_{CEQ} = 4 \text{ mA}.1 \text{ k}\Omega + 9 = 13 \text{ V}$$

$$I_{C}(t)_{Max} = I_{CQ}R_{ac} + V_{CEQ} = 4 \text{ mA}.1 \text{ k}\Omega + 9 = 13 \text{ V}$$

$$I_{C(t)_{Max}} = I_{CQ}R_{ac} + V_{CEQ} = 4 \text{ mA}.1 \text{ k}\Omega + 9 = 13 \text{ V}$$

$$I_{C}(t)_{Max} = I_{CQ}R_{ac} + V_{CEQ} = 4 \text{ mA}.1 \text{ k}\Omega + 9 = 13 \text{ V}$$

$$I_{C}(t)_{Max} = I_{CQ}R_{ac} + V_{CEQ} = 4 \text{ mA}.1 \text{ k}\Omega + 9 = 13 \text{ V}$$

$$I_{C}(t)_{Max} = I_{CQ}R_{ac} + V_{CEQ} = 4 \text{ mA}.1 \text{ k}\Omega + 9 = 13 \text{ V}$$

$$I_{C}(t)_{Max} = I_{CQ}R_{ac} + V_{CEQ} = 4 \text{ mA}.1 \text{ k}\Omega + 9 = 13 \text{ V}$$

$$I_{C}(t)_{Max} = I_{CQ}R_{ac} + V_{CEQ} = 4 \text{ mA}.1 \text{ k}\Omega + 9 = 13 \text{ V}$$

$$I_{C}(t)_{Max} = I_{CQ}R_{ac} + V_{CEQ} = 4 \text{ mA}.1 \text{ k}\Omega + 9 = 13 \text{ V}$$

$$I_{C}(t)_{Max} = I_{CQ}R_{ac} + V_{CEQ} = 4 \text{ mA}.1 \text{ k}\Omega + 9 = 13 \text{ V}$$

$$I_{C}(t)_{Max} = I_{CQ}R_{ac} + V_{CEQ} = 4 \text{ mA}.1 \text{ k}\Omega + 9 = 13 \text{ V}$$

$$I_{C}(t)_{Max} = I_{CQ}R_{ac} + V_{CEQ} = 4 \text{ mA}.1 \text{ k}\Omega + 9 = 13 \text{ V}$$

$$I_{C}(t)_{Max} = I_{CQ}R_{ac} + V_{CEQ} = 4 \text{ mA}.1 \text{ k}\Omega + 9 = 13 \text{ V}$$

$$I_{C}(t)_{Max} = I_{CQ}R_{ac} + V_{CEQ} = 4 \text{ mA}.1 \text{ k}\Omega + 9 = 13 \text{ V}$$

$$I_{C}(t)_{Max} = I_{CQ}R_{ac} + V_{CEQ} = 4 \text{ mA}.1 \text{ k}\Omega + 9 = 13 \text{ V}$$

$$I_{C}(t)_{Max} = I_{CQ}R_{ac} + V_{CEQ}R_{ac} + V$$

# **Example -Continued**

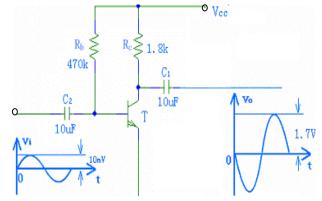

#### **Graphical Analysis**

- Can be useful to understand the operation of BJT circuits.

- First, establish DC conditions by finding  $I_B$  (or  $V_{BE}$ )

- Second, figure out the DC operating point for  $I_C$

Can get a feel for whether the BJT will stay in active region of operation

– What happens if  $R_C$  is larger or smaller?

$$v_{ce} = -i_{c}(R_{C} /\!/ R_{L}) = -i_{c}R_{L}$$

$$V_{CC}' = V_{CEQ} + I_{CQ}R_L'$$

#### **Graphical Analysis**

Q-point is centered on the ac load line:

V<sub>cc</sub>

R¢

Vcc.

Rα

Rъ

**6.2 Single-Stage BJT Amplifiers**

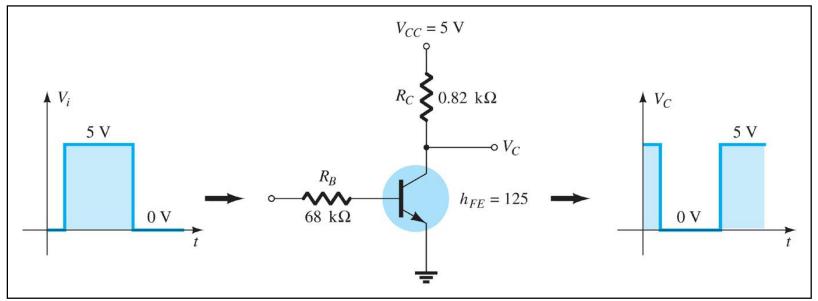

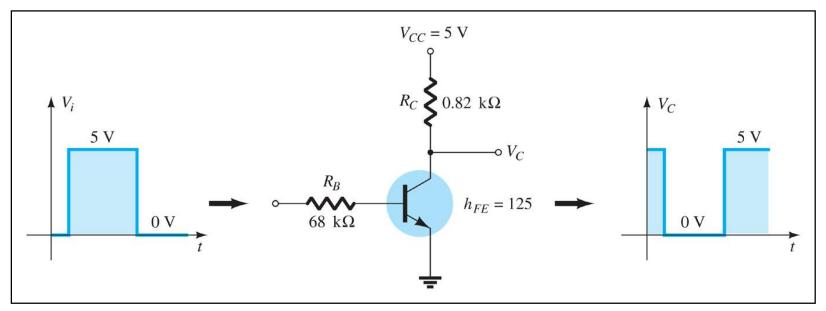

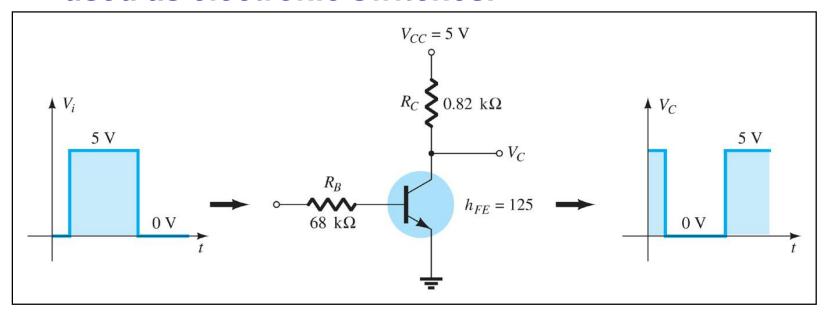

# **Transistor Switching Networks**

Transistors with only the DC source applied can be used as electronic switches.

For

$$Vi = 5V$$

$$I_{\rm B} = \frac{5 - 0.7}{68k\Omega} = 63.24 \ \mu A$$

$$I_C = (125)(63.24 \,\mu\text{A}) = 7.9 \,\text{mA}$$

$$V_{CE} = V_{CC} - I_{C}R_{C}$$

$$= 5 - (7.9 \text{ mA})(0.82 \text{k}\Omega)$$

$$= -1.482 \text{V} < V_{CE(\text{sat})}$$

$\therefore$  BJT is in Sat. Mode & Vc = V<sub>CE(sat)</sub>

## **Transistor Switching Networks**

Transistors with only the DC source applied can be used as electronic switches.

$$I_{C(sat)} = \frac{5}{0.82 \text{ k}\Omega} = 6.1 \text{ mA}$$

$$V_{O} = V_{CE(sat)} \cong 0.2 \text{ V}$$

## **Transistor Switching Networks**

Transistors with only the DC source applied can be used as electronic switches.

For

$$Vi = 0V$$

$$I_B = 0$$

$$I_C = 0$$

$$V_{CE} = V_{CC}$$

:. BJT is in Cut - off Mode &

$$Vc = V_{CE(cut0ff)} = V_{CC} = 5V$$